| Indeks | English version |

| Końcówka | Symbol | Funkcja |

|---|---|---|

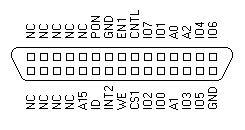

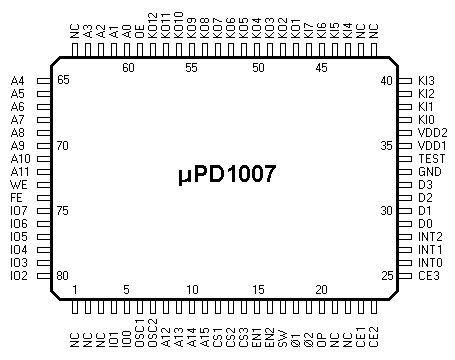

| 75..80 4,5 | IO7..IO0 | dwukierunkowa szyna danych |

| 6,7 | OSC1,OSC2 | rezonator ceramiczny 910kHz, OSC2 jest wyjściem inwertera oscylatora |

| 8..11 | A12..A15 | szyna adresowa |

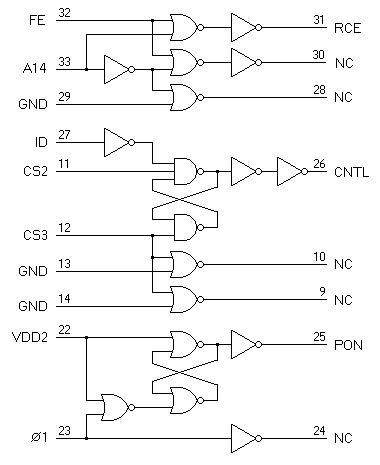

| 12..14 | CS1..CS3 | wyjścia Chip Select wybierające dodatkowe banki pamięci, aktywny niski poziom. CS1: interfejs FA-80 CS2,CS3: jednobitowy port wyjściowy CNTL w gate array uPD65005G-045 |

| 15 | EN1 | jednobitowy port wyjściowy, niski poziom załącza zasilanie systemu |

| 16 | EN2 | jednobitowy port wyjściowy podłączony do wejśia INT0, umożliwia programowe generowanie przerwań |

| 17 | SW | wejście wyłącznika zasilania, łączone do VSS (włączone) albo do GND (wyłączone) |

| 18,19 20 23..25 29..32 |

Ø1,Ø2 OP CE1..CE3 D0..D3 |

magistrala sterownika wyświetlacza, podobna jak w Casio FX-700P, zanegowana logika wszystkich sygnałów, wyjścia CE2 i CE3 nie są wykorzystane w FX-8000G |

| 26 | INT0 | wejście zewnętrznych przerwań sterowane z końcówki EN2 |

| 27 | INT1 | wejście zewnętrznych przerwań, dostaje impulsy z końcówki 27 układu sterownika wyświetlacza HD44352 |

| 28 | INT2 | wejście zewnętrznych przerwań, używane przez interfejs FA-80 |

| 33 | GND | plus zasilania |

| 34 | TEST | |

| 35 | VDD1 | minus zasilania (na stałe) |

| 36 | VDD2 | minus zasilania (wyłączany) |

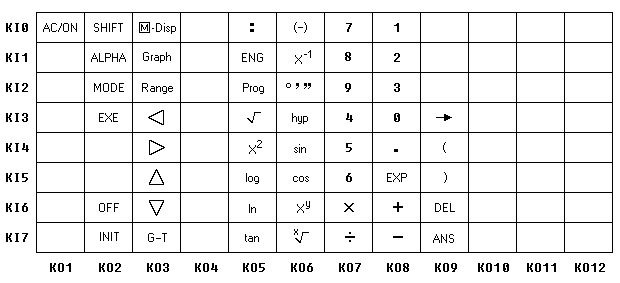

| 37..40, 43..46 | KI0..KI7 | port wejściowy matrycy klawiatury, dostępny przez rejestr KI |

| 47..58 | KO1..KO12 | port wyjściowy matrycy klawiatury, sterowany przez rejestr KO |

| 74 | OE | sygnał odczytu, aktywny niski poziom |

| 60..63, 65..72 | A0..A11 | szyna adresowa |

| 73 | WE | sygnał zapisu, aktywny niski poziom |

| 74 | FE | sygnał Chip Select pamięci, aktywny niski poziom |

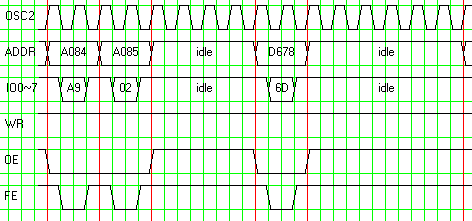

A084: A9 02 LD R2,(IY)+

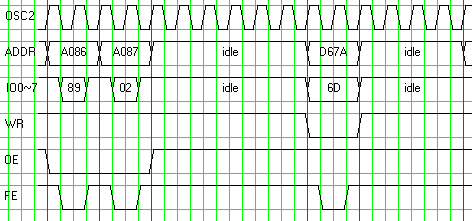

A086: 89 02 ST +(IY),R2

Kolumny matrycy klawiatury są wybierane przez 12-bitowy port wyjściowy KO. Wciśnięty klawisz łączy wybraną kolumnę z jednym z wierszy. Linie wierszy są odczytywane przez 8-bitowy port wejściowy KI.