| Indeks | English version |

Przedstawione urządzenie umożliwia transfer danych pomiędzy kalkulatorem FX-8000G i komputerem PC za pomocą portu szeregowego. Nie jest kompatybilne z oryginalną przystawką FA-80.

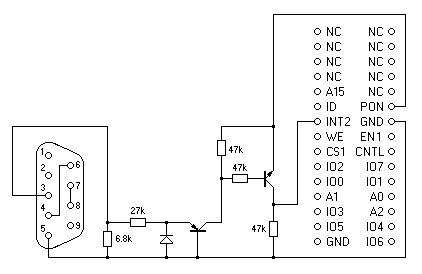

Schemat interfejsu dla portu RS232. Może tylko przesyłać dane do kalkulatora.

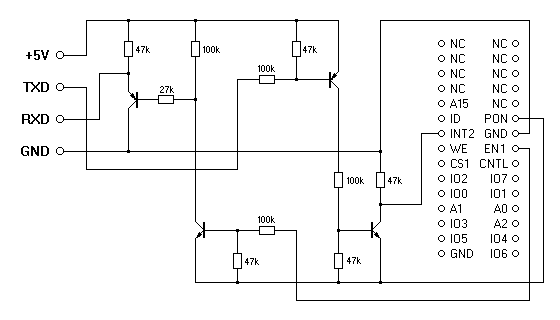

Schemat interfejsu dla poziomów logicznych 5V. W celu podłączenia do portu RS232 lub USB wymagany jest dodatkowy konwerter zbudowany np. na układzie MAX232 (RS232) lub FT232R (USB).

Programy przesyłające dane napisane zostały w języku asembler. Metoda wpisywania i uruchamiania programów maszynowych na kalkulatorze FX-8000G opisana jest na osobnej stronie.

Program odczytuje dane z portu szeregowego do pamięci edytora plików. Transmisja zostaje zakończona wciśnięciem klawisza DEL lub gdy wystąpił błąd.

2→S Hex 60B78A40:Prog 0 C00041C7:Prog 0 7C600F99:Prog 0 4802C300:Prog 0 C0847114:Prog 0 49F9822C:Prog 0 82087C5A:Prog 0 FA41081A:Prog 0 0BF10174:Prog 0 5B085EF1:Prog 0 0FF9820C:Prog 0 82082B82:Prog 0 01FE00FA:Prog 0 FA03F101:Prog 0 745B088C:Prog 0 000BF101:Prog 0 745B25F9:Prog 0 822C8208:Prog 0 7C5AFA70:Prog 0 B1880000:Prog 0

Fragmenty kodu, które zawierają w komentarzu liczbę taktów, muszą być wykonane w ściśle określonym czasie. Nie powinny być one modyfikowane w sposób, który by wpływał na czas wykonania.

ORG &H5AE8

BEGIN: CAL &HB78A ;"LOAD executing"

LDW IX,&HC000

LDW IY,&HC77C

CAL &H0F99 ;zapełnienie pamięci RAM od adresu IX do IY wartością &HFF

ADW IX,2 ;IX = &HC77D

PST IE,&H00 ;zablokowanie przerwań

PST KO,&H84 ;wybrane wyjście portu klawiatury KO9

; czekanie na bit startu

LOOP1: JMP K,&H1449 ;10 taktów, "Break" gdy wciśnięty klawisz DEL

; powinno zająć ok. 1.5*379 taktów od tego miejsca do BIT1

GST R2,IF ;8 taktów

TAN R2,&H08 ;10 taktów

JMP Z,LOOP1 ;10 taktów

; został wykryty bit startu

LDW IY,&H081A ;10 taktów, R121 = licznik bitów, R57 = opóźnienie

; pętla odbierająca bity, powinna zająć 379 taktów stąd do STORE

LOOP2:

DEL2: SB R57,1 ;10 taktów

JMP NZ,DEL2 ;10 taktów

LD R57,15 ;10 taktów, opóźnienie

; powinno zająć 379 taktów od tego miejsca do STOP1

BIT1: GST R2,IF ;8 taktów

AN R2,&H08 ;10 taktów

TSB R2,1 ;10 taktów, odbierany bit bit -> Carry

ROD R0 ;8 taktów, R0 = odbierany bajt

NOP ;6 taktów

NOP ;6 taktów

; następny bit

SB R121,1 ;10 taktów

JMP NZ,LOOP2 ;10 taktów

; zapis odebranego bajtu do pamieci

STORE: ST -(IX),R0 ;16 taktów

DEL3: SB R57,1 ;10 taktów

JMP NZ,DEL3 ;10 taktów

; sprawdzenie obecności bitu stopu

STOP1: GST R2,IF

TAN R2,&H08

JMP Z,LOOP1 ;następny bajt, gdy nie wystąpił błąd ramki

JMP &HB188 ;"I/O error"

Program wysyła przez port szeregowy zawartość pamięci RAM. Transmisja może zostać przerwana klawiszem DEL.

2→S Hex 60B77B40:Prog 0 C000C300:Prog 0 C0847114:Prog 0 495E8203:Prog 0 A801FC81:Prog 0 405F8B90:Prog 0 0B830174:Prog 0 5B00FE02:Prog 0 FE01775B:Prog 0 12C10070:Prog 0 5AFDC101:Prog 0 745AFD23:Prog 0 F0E0775A:Prog 0 F2701449:Prog 0

ORG &H5AE8

BEGIN: CAL &HB77B ;"SAVE executing"

LDW IX,&HC000

PST IE,&H00 ;zablokowanie przerwań

PST KO,&H84 ;wybrane wyjście portu klawiatury KO9

; pętla wysyłająca bajty

LOOP1: JMP K,&H1449 ;"Break" gdy wciśnięty klawisz DEL

LD R2,&H03 ;2 bity stopu

LD R1,(IX)+

BIUM R1..R2 ;bit startu

; pętla wysyłająca bity, powinna zająć 379 taktów (=910000kHz/2400baud)

LOOP2: LDM R3..R4,16 ;14 taktów, zapis do R4 tylko dla nabicia taktów

DEL: SB R3,1 ;10 taktów

JMP NZ,DEL ;10 taktów

; w tym momencie bit Carry jest skasowany

ROD R2 ;8 taktów

ROD R1 ;8 taktów, wysyłany bit -> Carry

JMP C,ONE ;10 taktów

PST IF,&H00 ;8 taktów

JMP LOOP2 ;10 taktów, następny bit

ONE: PST IF,&H01

JMP NZ,LOOP2 ;następny bit

; następny bajt

TSB R120,&HE0 ;koniec pamięci RAM?

JMP C,LOOP1 ;następny bajt jeżeli nie

JMP &H1449 ;"Break"