| Indeks | English version |

Na tej stronie opisane są tylko szczegóły charakterystyczne dla FX-870P. Ogólniejsze informacje na temat mikroprocesora i magistrali są dostępne w opisie sprzętu PB-1000.

CS0: &H00C00..&H0FFFF oraz &H20000..&H2FFFF, pamięć ROM 128kB

CS1: &H34000..&H37FFF, nie używane

CS2: &H30000..&H30001, nie używane

CS3: &H38000..&H3FFFF, złącze urządzeń peryferyjnych

CS4: &H32000..&H33FFF, nie używane

CS5: &H31000..&H31FFF, nie używane

CS6: &H10000..&H1FFFF, gate array (przestrzeń adresowa pamięci RAM)

CS7: &H30000..&H30007, gate array (rejestry)

P7..P6 sterują głośniczkiem piezoelektrycznym

P5 jest wejściem BUSY portu drukarki

P4 wybiera wersję językową, może być połączony za pomocą zworki PAD3 do +5V (wersja japońska) lub za pomocą zworki PAD4 do GND (jakaś nie produkowana wersja eksportowa)

P3 jest wyjściem STROBE portu drukarki

P2 jest wyjściem INIT portu drukarki

P1 jest nie używany

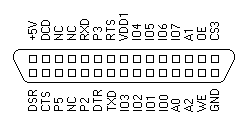

P0 dostaje wysoki poziom napięcia z układu monitora baterii S8054ALR gdy obecne jest prawidłowe napięcie zasilające

Sygnały zegarowe Ø1 i Ø2 są rozprowadzane do urządzeń peryferyjnych poprzez cewkę pupinizacyjną.

W przeciwieństwie do PB-1000 i PB-2000C, kalkulator FX-870P ma minus zasilania na masie (GND).

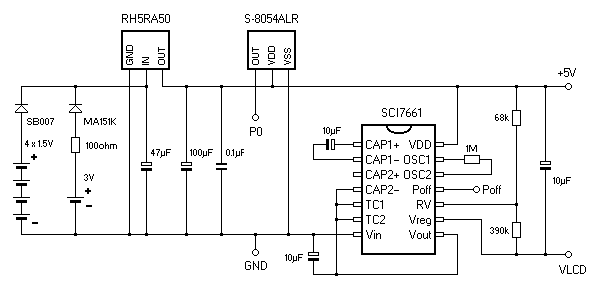

| Końcówka | Symbol | Funkcja |

|---|---|---|

| 1 | Poff | steruje wejściem Poff układu scalonego przetwornicy napięcia SCI7661 |

| 20 | VDD1 | dostaje niski poziom z końcówki 33 mikroprocesora gdy kalkulator jest włączony |

| 23 | OPT1 | wybiera konfigurację pamięci RAM, może być połączony za pomocą zworki PAD1 do +5V (wlutowana na płytce pamięć 8kB) lub za pomocą zworki PAD2 do GND (wlutowana na płytce pamięć 32kB) |

| 24 | WR | sygnał strobu zapisu, aktywny niski poziom |

| 25 | OE | sygnalizuje ważne dane |

| 27 28 | Ø2 Ø1 |

dwufazowy sygnał zegarowy z mikroprocesora |

| 29 | INT1 | wyjście zgłoszenia przerwań, aktywny niski poziom |

| 30 | CS7 | wejście chip enable dla rejestrów gate array, dostaje niski poziom z mikroprocesora w zakresie adresów &H30000..&H30007 |

| 31 | CS6 | wejście chip enable dla przestrzeni adresowej pamięci RAM, dostaje niski poziom z mikroprocesora w zakresie adresów &H10000..&H1FFFF |

| 32..39 | IO7..IO0 | dwukierunkowa szyna danych |

| 40..41 | A0, A1 | wejścia szyny adresowej |

| 43..47 | A2, A12..A15 | wejścia szyny adresowej |

| 48..50 | XA12..XA14 | wyjścia szyny adresowej dla pamięci RAM, taki sam stan jak A12..A14 gdy OPT1 ma wysoki poziom, lub po odjęciu przesunięcia &H3000 od adresu wysłanego przez mikroprocesor gdy OPT1 ma niski poziom To przeliczanie adresów jest zbędne, system działałby równie dobrze z pamięcią RAM podłączoną bezpośrednio do szyny adresowej mikroprocesora. |

| 55 | TXD | dane wysyłane przez port szeregowy |

| 56 57 | RTS DTR |

sygnały sterujące portu szeregowego |

| 59 | RXD | dane odbierane przez port szeregowy |

| 60 61 62 | CTS DSR CD |

sygnały statusu portu szeregowego |

| 63 | XCS0 | wyjście chip enable dla wlutowanej na płytce pamięci RAM, dekodowany zakres adresów &H11000..&H12FFF gdy OPT1 ma wysoki poziom, lub &H10000..&H17FFF gdy OPT1 ma niski poziom |

| 64 | XCS1 | wyjście chip enable dla modułu rozszerzenia pamięci RAM, dekodowany zakres adresów &H13000..&H1AFFF gdy OPT1 ma wysoki poziom, lub &H18000..&H1FFFF gdy OPT1 ma niski poziom |

| A2 | A1 | A0 | Dostęp | Funkcja |

|---|---|---|---|---|

| 0 | 1 | 0 | Odczyt | rejestr wejściowy portu szeregowego |

| Zapis | rejestr wyjściowy portu szeregowego | |||

| 0 | 1 | 1 | Odczyt | bit 0 - ustawiony gdy nadajnik gotowy do przyjęcia danej bit 1 - znacznik odebrania bajtu, kasowany przez odczytanie rejestru 010 bit 2 bit 3 - ustawiany przez błąd parzystości bit 4 - ustawiany przez błąd przepełnienia bit 5 - ustawiany przez błąd bitu stopu |

| Zapis | bit 0 bit 1 bit 2 - ustawiony dla 8 bitów danych, skasowany dla 7 bitów danych bit 3 bit 4 - ustawiony włącza kontrolę parzystości/nieparzystości bit 5 - wybór kontroli parzystości gdy ustawiony, nieparzystości gdy skasowany bit 6 - ustawiony dla tej funkcji bit 7 - ustawiony dla 2 bitów stopu, skasowany dla 1 bitu stopu | |||

| bit 0 bit 1 - stan wyjścia RTS (zanegowany) bit 2 bit 3 bit 4 bit 5 - stan wyjścia DTR (zanegowany) bit 6 - skasowany dla tej funkcji bit 7 | ||||

| 1 | 0 | 0 | Odczyt/Zapis | bit 0..2 - szybkość transferu przez RS232C i wysyłania do MT bit 3 bit 4 bit 5 - ustawiony dla odczytu z MT w trybie Slow, skasowany w trybie Fast bit 6 - uaktywnienie odbiornika bit 7 - uaktywnienie nadajnika |

| 1 | 0 | 1 | Odczyt/Zapis | bit 2 - ustawiony dla MT, skasowany dla RS232C bit 4 - inwersja wczytywanego sygnału MT |

| 1 | 1 | 0 | Odczyt | bit 0 - ustawiony przy obecności prawidłowego sygnału "pilota" z magnetofonu bit 2 - stan wejścia CTS (zanegowany) bit 3 - stan wejścia DSR (zanegowany) bit 4 - stan wejścia DCD (zanegowany) bit 7 - stan wejścia OPT1 |

| Zapis | ||||

| 1 | 1 | 1 | Odczyt/Zapis |

| bity 210 |

baud rate |

|---|---|

| 001 | 4800 |

| 010 | 2400 |

| 011 | 1200 |

| 100 | 600 |

| 101 | 300 |

| 110 | 150 |

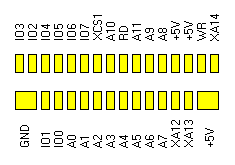

01 - GND 02 - +5V 03 - VLCD 04 - ON 05 - Ø1 06 - Ø2 07 - OP 08 - CE1 09 - CE2 10 - VDD2 11 - D0 12 - D1 13 - D2 14 - D3 15 - GND |

01 - GND 02 - KI12 03 - KI11 04 - KI10 05 - KI9 06 - KI8 07 - KI7 08 - KI6 09 - KI5 10 - KI4 11 - KI3 12 - KO1 13 - KO2 14 - KO3 15 - KO4 16 - KO5 17 - KO6 18 - KO7 19 - KO8 20 - KO9 |

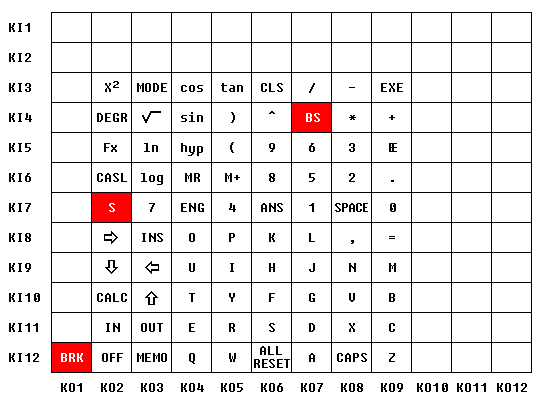

Kolumny matrycy klawiatury są wybierane przez 12-bitowy port wyjściowy KO, sterowany za pomocą rejestru IA. Wciśnięty klawisz łączy wybraną kolumnę z jednym z wierszy. Linie wierszy są odczytywane przez 12-bitowy port wejściowy KI, dostępny poprzez rejestr KY.

Relacja pomiędzy bitami rejestru KY a wierszami klawiatury:

![]()